# A Synchronous Barrel Shifter Design Using Single Rail and hybrid Rail logic

## SowmyaPC1, KripamolCA2

<sup>1</sup>AssistantProfessor, ECE, IES College of Engineering, Chittilappilly, Kerala, India. <sup>2</sup>Student, ECE, IES College of Engineering, Chittilappilly, Kerala, India.

### How to cite this paper:

SowmyaPC<sup>1</sup>, KripamolCA<sup>2</sup>. A Synchronous Barrel Shifter Design Using Single Rail and hybrid Rail logic", IJIRE-V4I03-33-38.

Copyright © 2023 by author(s) and 5th Dimension Research Publication. This work is licensed under the Creative Commons Attribution International License (CC BY 4.0).

http://creativecommons.org/licenses/by/4.0/

Abstract: A plan for an asynchronous Single Rail and Hybrid Rail logic barrel shifter hardware is proposed in this undertaking. A packaged information asynchronous circuit is innately liberated from difficulties related with clock signals, however it is absent any and all data relating to spread postpone through the circuit. A conspicuous arrangement is to deliver the recognize signal in any event  $\delta$  postpone units after the appearance of the solicitation signal, where  $\delta$  is the greatest spread defer through the circuit. In a Half breed rail idea there is no defer estimation circuit. Be that as itmay, like simultaneous circuits, such group information asynchronous approach doesn't exploittimes where the engendering defer through the circuit is not exactly  $\delta$ . This brief proposes a plan fora deterministic culmination identification conspire for an asynchronous packaged information barrelshifter. When the solicitation signal is dynamic, the moving activity starts, and the recognize signalis produced after a postpone that coordinates the genuine moving deferral related with the shift sumutilizing a deterministic fruition recognition plot. The shifter can lessen the inactive time betweenthe time its result is prepared and the beginning of the following movement cycle by utilizing a de-terministic culmination location circuit. In this short, the proposed plan of the asynchronous barrel shifter and its typical deferral is broke down. Its exhibition is likewise analyzed against its simulta-neous partner.

Key Word: Asynchronous circuit design, barrel shifter, deterministic completion detection circuitry, bundled-data protocol, Hybrid logic data protocol

#### **I.INTRODUCTION**

Advanced circuits configuration styles can be arranged into coordinated and offbeat classes. In simultaneous plan, the framework comprises of modules every one of them are constrained by atleast one synchronizer clock signals. coordinated circuits are made out of combinational circuits andregisters. The circuit action is constrained by a worldwide clock which triggers simultaneously theremembrance of the total condition of the circuit. As another state is tested and set in the registers, the combinational circuits start the calculation of the following state to be examined at the follow-ing clock edge. This is predictable with the so called register move level detail (RTL) formalism uti-lized by the majority of the architects today.

The reception of such a model has three significant results on the plan of these circuits:

- i) combinational rationale is straight forward in light of the fact that perils are over looked,

- ii) The Correspondence system between the parts is minor

- iii) There is a world wide timing expectation to regard for the circuit to be functional: the longest combinational way (basic way) shouldn't surpass the clock time frame.

Exceptionally huge reconciliation of rationale doors on single kick the bucket along side the contracting of semiconductor size in late coordinated circuit advancements prompts a muddled clock organization. This worldwide clock network has a few difficult issues, for example, clock sig-nal deferral and slant. These issues forest all the conventional clock recurrence expanding pattern inIC assembling. Because of the rising constraints and developing intricacy of semi-custom coordi-nated plan, asynchronous circuits areacquiring in interest.

There are some distinctive benefits for asynchronous circuits as follows: low power utilization due to fine-grain clock gating and zero backup power utilization, high working pace because of assurance of circuit defer by nearby latencies as opposed to worldwide most pessimistic scenario dormancy, less discharge of electro-attractive clamor because of the hap hazardness of neighborhood clock's rising and falling occasions in time, heartiness towards varieties in supply voltage, tempera-ture, and creation process boundaries, entry ways and wires' postpone obtuse timing depends on paired delay, better composability and measured quality as a result of the straight forward hand shake interfaces and the nearby. Without even a trace of a worldwide clock that controls register and state refreshing, asynchronous configuration depends on hand shaking to move information between utili-tarian blocks. In these circuits, the stages have two sections. Initial segment is controlling circuit for hand shaking with neighbor stages and second is information way circuit for handling information.

## **II.RELATED WORK AND MOTIVATION**

One method for managing a monstrous shift sum is to carry out the shifter equipped formoving an erratic number of

ISSN No: 2582-8746

pieces in a solitary clock cycle [1]. These shifters are ordinarily com-prised of different stages with each phase of the shifter moving its contribution by a decent number of spots. One of the earliest references to such shifter configuration is for the CDC 6600 PC in themid 1970s [2]. A comparable plan [3] was used by Intel without precedent for a numeric information processor [4] and were called Barrel Shifters – the expression "barrel" as in the barrel of a fire arm which moves everything its substance as one at whatever point the barrel is pivoted.

Throughout the long term, a few plan plans have been proposed to work on the exhibition of barrel shifters [5], [6]. The majority of there the most extreme clock not entirely set in stone by con-sidering the most pessimistic scenario postpone through every calculation component. In any case, the interest for quicker and more reduced electronic gadgets fuel interest for innovation scaling that just worsen the hardships related with clock slanting. The interest for versatile electronic gadgets with negligible power utilization, without compromising handling velocity and silicon region is amain pressing issue [7], [8]. asynchronous circuits, where circulated restricted handshaking signalsare utilized instead of worldwide clock signal(s), are liberated from difficulties connected with clock slanting.

## III.BARREL SHIFTER

Shifter circuits are normally tracked down in advanced frameworks. Shifter can be planned utilizing flip-flops organized as shift registers, where it plays out a the slightest bit shift in one clock cycle. The handling season of such shifters is straight forwardly corresponding to the shift sum, i.e.,n clock cycles would be expected to move an info information by n-bits. The dormancy of this plan makes it unfeasible when n is huge – a condition generally found in complextasks like drifting point expansion, DSP, encryption applications, andso on.

A barrel shifter has n information inputs, n information yields and a bunch of control inputsthat indicate how to move the information inputs. The control inputs indicate the kind of shift (intel-ligent, mathor round-round about shift is typically assigned pivot), the course of the shift (left or right), and how much shift (from 0 to n - 1). When applied to the information inputs, the moving ac-tivities have the accompanying way of behaving: SRL - Shift right sensible: performs m-piece right shift and sets the upper m pieces to zeros. SRA - Shift right number-crunching: performs m-pieceright shift and sets the upper m pieces to the main piece to carry out sign augmentation. SRC - Shift right round: performs m-piece passed on shift and sets the upper m pieces to the lower pieces of the in-formation. SLL - Shift left intelligent: performs m-piece passed on shift and sets the lower m pieces to zeros. SLA - Shift left number juggling: performs m-piece passed on shift and sets the lower m pieces to zeros. SLC - Shift left round about: performs m-piece left shift and sets the lower m pieces of the result to the higher pieces of the info. Consider, for instance, an 8-digit barrel shifter with in-formation inputs17-0, information yields 070, and a3-cycle contribution to determine the shift sum, mE[0, 7].

The association of there mainder of this brief is as per the following: The fundamentals to the asynchronous configuration plot and forms the specialized difficulties. The principal commit-ment of this brief is the proposed plan for a packaged information asynchronous barrel shifter with deterministic finish discovery capacity that has a typical proliferation defer that is not exactly the worst-case postpone tracked down in its simultaneous partner. The proposed plan is broke down and its exhibition looked at against its coordinated partner with regards to a drifting point viper as a way to show the possible benefit of the proposed plan for continuous applications.

## IV. PROPOSED SOLUTION: AN ASYNCHRONOUS BUNDLED DATA BARREL SHIFTER

This part sums up the fundamentals connected with the traditional barrel shifter plan and the asynchronous design scheme. The detailing of the exploration question is drawn from these starters.

Documentation: Factors  $S,I,n,s,j,k,\lambda,\in Z+$ ; Sime ansthe select line for all multiplexers present instage Iofann-bit Ordinary Barrel Shifter(CBS). Variables addresses the shift measure of an-bit CBS with the end goal that  $0 \le s < n$ . The variable  $\lambda$  means the absolute number of shift stages ex-pected to move the info information I by s-bits utilizing an n-cycle CBS. I = I0I1  $\cdots$ In-1 addresses ann-bit of info information to be moved, and Y=Y0Y1  $\cdots$ Yn-1 addresses the comparing moved n bit yield information.

Req and Ack signifies the hand shaking demand and recognize flags separately. A solitary CBS stage I is carried out utilizing n  $2 \times 1$  multiplexers, consequently the complete number of  $2 \times 1$  multiplexers expected to execute a n-bit CBS is n  $\times \lambda$ , where  $\lambda$  is the all out number of CBS stagesand  $\lambda = log2n$ . The info information I is constantly associated with the CBS stage 0, and the lastmoved yield is caught from the CBS stage n-1. The contribution of a moderate stage I is associated with the result of its past stage I -1, and its result is associated with the contribution of its nextstage I +1. An individual CBS stage I can either move the info information I by a specific sum, or pass the information to the following stage without moving, contingent on the worth of the selectline Si relating to a shift sum s. The shift sum s can be communicated as continues as far as the se-lect lines of the CBS stages.

The engendering delay through a CBS is the time it takes for information at its contribution to cross through the  $\lambda$  multiplexer phases of the CBS. As needs be, on the off chance that  $\delta s$  is the proliferation delay for a solitary phase of the CBS, the engendering delay for a CBS, which is like-wise themost pessimisticscenario delay, is given as  $\delta c$  bs.

At the point when utilized in a simultaneous circuit, the spread postponement for a CBS willbe fixed at  $\delta$ CBS regardless of the quantity of multiplexer arranges that is expected to play out the shift or when the information at its result is prepared. A similar CBS setup,on the off chance that utilized in an asynchronous circuit, will require a method for deciding when the information at its result is prepared. The clearest arrangement is to ensure that the information at the contribution of the CBS is prepared prior to affirming the req signal and the ack signal is just stated  $\delta$ CBS after the declaration of the req signal. This plan, by and large delegated packaged information or single-railcoding, can't use the situations when yield information can be prepared preceding the most pes-simistic scenario defer  $\delta$  CBS.

An elective way to deal with identify fulfillmentist outilize dual-rail coding where each sign is carried out alongside its correlative rationale, making it conceivable to code the informationas 0, 1 and invalid. Double rail convention inserts the data of interaction finish with the actual infor-mation; a cycle will begin with all information as invalid and culmination is naturally demonstrated when everyone of its results are legitimate. Noneheless, an extra circuitis expected to recognize the legitimacy of the result information adding additional handling time after the result is prepared, bringing about a postpone above of processing information legitimacy on top of the genuine calcu-lationdelay.

Single-rail packaged information executions, then again, don't experience the ill effects of the area punishment of double rail plan and can exploit the early finishing time, if there is a way todecide the handling time expected by the circuit to deal with its bits of feedbacks. Later a compara-ble procedure is utilized to carry out coordinated and off beat barrel shifter. This approach detailed an improvement in execution, because of its capacity to identify early finishing, going from 5% to 30% over a tant amount coordinated execution. Be that as it may, the presentation of a speculative finishing discovery method is profoundly subject to the productivity of the cut short organization, which is utilized toend the misle ading setting off for a nearly fulfillment.

Lai, fostered an asynchronous packaged information viper utilizing an early culmination lo-cation strategy which dispenses with the requirement for cut short organization, in this way speed-ing up by 8-10%. This brief proposes a deterministic way to deal with plan an asynchronous barrel shifter utilizing a packaged information convention to such a nextent that,

- The proposed finish identification strategy is deterministic, and the shifter can identify the interaction fruition without the requirement for a cut short organization.

- The cut short organization is a basic part of the speculative plan plot that adds rationale pro-fundity and deferral to the computerized circuit, and eliminating it further develops the cir-cuit execution fundamentally. The design of the proposed asynchronous Bundled data Barrel Shifter (ABBS) with a deterministic fulfillment recognition method is like wise examined. The design of a solitary accuracy ABBS with a deterministic fulfillment recognition proce-dure is examined in this subsection, however a similar idea can be applied to any n-digit left as well as right shift barrel shifter. A 32-bit ABBS comprises of a 32-bit CBS and a Deterministic Fruition Discovery Circuit (DCDC), as displayed in Figure 2. A solitary accuracy CBS can be inherent the same way as the 8-bitCBS (allude Figure1), yet it can move 32-bit information by s-bits, where 0≤s≤31, with complete number of shift stagesλ= log232=5.

The DCDC is answerable for creating the ack signal when the moving activity is finished and the result information is legitimate. It comprises of a Result Choice Stage (OSS), a Shift Subor-dinate Selector (SDS), and a Postponement Creating Unit (DGU) that is intended to repeat the defer through the different shifter stages. OSS comprises of  $32.6 \times 1$  multiplexers (one for each piece ofthe information) and is utilized to channel inside stage result of the CBS for  $1 \le s \le 31$  or the info information for case s = 0. The information ways for these situations are featured in Figure 2 as ways way—s and way—0,individually. The last result of the ABBS is caught from the OSS stage with the assistance of its 3-digit select lines, when the dynamic shifter stage(s) relating to the shift sum have been distinguished.

SDS is answerable for unraveling the quantity of dynamic shifter stage(s) for the given shiftsum and choosing the comparing defer way from DGU. A SDS is designed with 32 memory areas, every one of which is 9-bits wide for a solitary accuracy ABBS, as determined in Table I. The 5-digit shift sum is given to the SDS input, which goes about as an exceptional location of these mem-ory areas (25 = 32) relating to the shift sum. The term SDS yield alludes to the 9-cycle information put away in these memory areas. The initial three least critical pieces of SDS yield are associated with the select lines of OSS, as shown by the sub way oss of the sign way SDS. This permits theOSS to choose the earliest inner sign inside the CBS known to convey the legitimate result esteem. For example, OSS chooses the non-moved 32-digit input information when these 3 pieces has aworth of 000, the result of the main CBS shift stage in the event that these 3 pieces has a worth of001, the result of the second CBS shift stage in the event that these 3 pieces have a worth of 010, etc.

The left over six pieces of SDS yield are utilized to choose the postpone way from DGU re-lating to the dynamic CBS stages related with a shift sum. DGU is answerable for stating the acksignal after spread delay related with the dynamic basic way of the shifter. DGU contains numerous defer models that are intended to duplicate the spread postponements of the different sign ways present in the shifter. A potential plan of the defer model utilizing the mix of As well as NOT doorsto repeat the multiplexer is displayed in Figure 3 with different postpone select data sources; D0 toD4 comparing 0 up to 4 CBS multiplexer stage delay, and DOSS relating the deferral of the OSSstage. It is vital to take note of that the defer model should have the option to precisely duplicate the postponement of the different multiplexer shift stages in the CBS.

A defer model that mis judges the genuine postpone will result in the ack signal being created later than it should be while a defer model that underrates the real defer required will result in the ack signal being declared rashly. In this lies the complexities of the plan of the postpone model con-sidering the need to coordinate the defer in the defer model with the circuits it is displaying, which might fluctuate at various cycle corners. Appropriately, it is suggested that the entryways utilized inthe defer model need to, best case scenario, precisely match and to say the least more slow than thecircuits the postpone model is duplicating. Thusly, it is recommended that the doors utilized in thepostpone model ought to one or the other be of a more vulnerable drive strength or have a greate rnumber of contributions than the genuine entryways in the shift stage being reproduced to guarantee that the proliferation defer through the defer model won't ever be not exactly the genuine shift stage delay.

By and by however, contingent upon how the ack signal is utilized, there might be other tim-ing contemplation between the ack signal and the legitimacy of the result information to consider.Information DOSS relating to OSS is dynamic for a 0-digit shift and the CBS is skipped. In likemanner, shift by 1-digit will include the primary poo stage and the OSS, thus D0 and DOSS are dy-namic.Likewise,a 2 and 3-cycle shiftwill require 2 shift stages and OSS, subsequentlyD0, D1,and DOSS are dynamic. Moreover, the settings of D4 to D0 and DOSS are sorted out for the othershift values. Table III gives the

postponement of dynamic datapath in ABBS, the relating dynamicDGU model related with a shift sum, and the distinction between the two for the 90nm library. The deferral of shifter and DGU is meant by factors  $\delta$  and  $\tau$ , individually. To stay away from untimely ack signal age, the postpone models should be somewhat more slow than the shifter, i.e.,  $\tau i > \delta i$  ( $0 \le I \le \lambda$ ) under every single state of being and for all infomixes.

#### V.PROPOSED SOLUTION

In asynchronous plan, the decision of handshake conventions influences the circuit execu-tion (region, speed, power, strength, and soon. The four- stage packaged information convention and the four-stage double rail convention are two famous conventions that are utilized in most prag-matic asynchronous circuits. The four-phase packaged information convention configuration most intently looks like the plan of simultaneous circuits. Handshake circuits create neighborhood clock heart beats and use delay matching to show legitimate sign. It typically prompts the most effective circuits because of the broad utilization of timing suppositions. Then again, the four-stage double rail convention configuration is executed in an intricate manner that the handshake signal is joined with the double rail encoding of information.

Handshake circuits know about the appearance of legitimate information by identifying the encoded handshake signal, which permits right activity within the sight of erratic information way delays. This element is extremely valuable for managing information way postpone varieties in cut-ting edge VLSI frameworks, for example, asynchronous field-programmable entry way exhibits (FP-GAs)and framework on-chip. Not withstanding, such appealing element is acknowledged to the detriment of encoding and location over heads. These over heads cause low circuit proficiency and limit the application region of the four-stage double rail convention plan. This paper presents an original plan strategy for asynchronous domino rationale pipeline, which centers around further de-veloping the circuit effectiveness and making off beat domino rationale pipeline plan more reason-able for a large number of uses. The original plan strategy joins the advantages of the four-stage double rail convention and the four-stage packaged information convention, which accomplishes a region proficient and ultra low-power asynchronous domin or ationale pipeline asynchronous domino rationale pipeline is an intriguing pipeline style that can totally stay away from express ca-pacity components between stages by taking advantage of the verifiable hooking usefulness of domino rationale entry ways.

The latchless element gives the advantages of diminished basic postponements, more mod-est silicon region, and lower power utilization. Not withstanding, asynchronous domino rationale pipeline has a typical issue that double rail domino rationale must be utilized to create the dominoinformationway. Single-rail dominorationale can't be utilized on the grounds that it would break the domino information way since just non-inverting rationale can be carried out. Subsequently, the domino information way has a double rail encoding above that consumes a ton of silicon region and power utilization. Such above nearly counter acts the region and power benefits given by the latch-less element. Another issue is the above of handshake control rationale. Traditional plans of asyn-chronous domino rationale pipeline in view of the four-stage double rail convention depend on domino information way to move information and encoded handshake sign, and use culmination identifiers to identify and gather the handshake signal all through the whole information ways. Suchplan technique is extremely powerful for defer varieties in information ways. Be that as it may, it causes a significant discovery above.

The recognition above is developing with the width of information ways, which obstructs its application in the plan of an enormous capability block with a significant information way width. Then again, off beat domino rationale pipeline in light of the four-stage packaged information con-vention dodges the location above by carrying out a solitary additional packaging signal, to match the most pessimistic scenario block delay, which fills in as a culmination signal. The issue is that this plan strategy totally loses the great properties in the four-stage double rail convention plan.

Moreover, it doesn't settle the double rail encoding above issue in information ways. In this paper, our proposed pipeline decreases both the double rail encoding above in information ways and thelocation above in handshake control rationale by planning in light of a developed basic information way. A stable basic information way is developed utilizing upgraded double rail domino entry ways. By distinguishing the stable basic information way, a 1-bit consummation locator is sufficient to getthe right handshake signal no matter what the information way width. Such plan doesn't just enor -mously lessen the recognition above yet additionally to some extent keeps up with the great proper-ties in the four-stage double rail convention plan.

Besides, the stable basic information way fills in as a matching deferral to settle the double rail encoding above issue in information ways. With the assistance of the updated double rail domino doors, single-rail domino rationale is effectively applied in non critical information ways. Thus, the proposed asynchronous domino rationale pipeline has a little above in both handshake control rationale and capability block rationale, which significantly further develops the circuit pro-ductivity. As per the plan include, we name the proposed pipeline as asynchronous pipeline in light of built basic information way (APCDP).

This paper is coordinated as follows. AreaII presents the foundation of asynchronous domino rationale pipeline. PS0 is acquainted with show the benefits and issues of asynchronous domino rationale pipeline in light of double rail convention. A few related plans are likewise basi-cally presented. Area III spotlights on the presentation of the proposed pipeline plan strategy. Syn-chronizing rationale entryways (SLGs) and synchronizing rationale doors with a lock capability (SLGLs) are acquainted with build as table basic information way.

The heartiness of the pipeline structure and the built basic information way is dissected. Then, at that point, more mind boggling pipeline structures are additionally talked about. SegmentIV presents the assessment results that show the advantages of the proposed pipeline contrasted and a bundled-data asynchronous domino rationale pipeline and a simultaneous pipeline with a succes-sive clock gating (Sync-CG). AreaV presents the end.

#### **VI.PSO**

- a significant starting point for most later proposed styles. Since our pro-posed pipeline is likewise founded on PS0, we will start by evaluating PS0 pipeline style, and after-ward essentially presenting two other high level styles:

- 1) A timing-hearty style called pre charge half-cradle

- 2) A high-throughput style called look ahead pipeline. At last, we outline the defer presumptions of these pipelines and give our postpone supposition in the proposed plan.

### **VII.RESULTS**

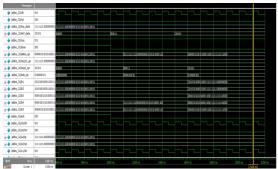

**i.** Existing System–Simulation result: The figure show that the simulation result of an asynchro-nous barrel shifter design using single rail logic.

Figure 7.1 Existing system-Simulation result

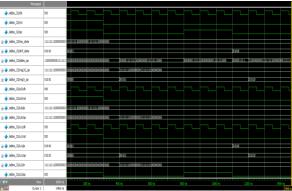

**ii. Proposed System–Simulation Result:** The figure show that the simulation result of an asyn-chronous barrel shifter design using Hybrid rail logic.

Figure 7.2 Proposed system-Simulation result

| Power summary:                     | I(mA) | P(mW |

|------------------------------------|-------|------|

| Total extimated power consumption: |       | 105  |

| Vecint 1.80V:                      | 55    | 98   |

| Vera33 3.30V:                      | 2     | 7    |

| Clocks:                            | 31    | 56   |

| Inputs                             |       | 15   |

| Logic:                             | 0     | 0    |

| Outputs:                           |       |      |

| Vero33                             | 0     | 0    |

| Signals:                           | 0     |      |

| Quiescent Vecint 1.50V:            | 15    | 27   |

| Quiescent Vcco33 3.30V;            | 1     | 7    |

| The read summary:                  |       |      |

| Estimated junction temperature:    |       | 27C  |

| Ambient temp:                      |       | 25C  |

| Case temps                         |       | 27C  |

| Theta J.A.                         |       | 17CW |

7.3 Existing System-Power and Thermal Summary

| Power summary:                     | I(mA) | P(mW) |

|------------------------------------|-------|-------|

| Total estimated power consumption: |       | 104   |

| Vecint 1.80V:                      | 54    | 97    |

| Vcco33 3.30V:                      | 2     | 7     |

| Clocks:                            | 30    | 55    |

| Inputs:                            | 8     | 15    |

| Logic:                             | 0     | 0     |

| Outputs:                           |       |       |

| Veco33                             | 0     | 0     |

| Signals:                           | 0     | 0     |

| Oniescent Vccint 1.89V:            | 15    | 27    |

| Quiescent Vcco33 3.30V:            | 2     | 7     |

|                                    |       |       |

| Thermal summary:                   |       |       |

| Estimated junction temperature:    |       | 27C   |

| Ambient temp:                      |       | 25C   |

| Case temp:                         |       | 27C   |

7.4 Proposed System–Power and Thermal Summary

## VIII.CONCLUSION

An offbeat barrel shifter configuration is carried out in this concise utilizing packaged information convention with a deterministic culmination location circuit and utilizing Hybrid information con-vention without a deterministic finishing recognition circuit. Two particular libraries are utilized to exhibit that the typical postpone expected by the proposed ABBS continuously applications is not exactly the most pessimistic scenario defer expected by the coordinated partner.

## A Synchronous Barrel Shifter Design Using Single Rail and hybrid Rail logic

#### References

- 1. An asynchronous FPGA In view of Double/Single-Rail Cross breed Engineering ERSA'12 ShortPaper ZhengfanXia, Shota Ishihara,Masanori Hariyama, and MichitakaKameyama GraduateSchoolof DataSciences,Tohoku College

- 2. S. M. Nowick, "Plan of a low-inertness asynchronous snake utilizing speculative finish," IEEProc.Comput. Digit.Techn., vol.143,no. 5,pp. 301-307, 1996.

- 3. K. K. Lai, "Novel offbeat fulfillment discovery for number-crunching data-paths," School Eng., Taylor's Univ., Subang Jaya, Malaysia, Rep., 2016.

- 4. K. K. Lai, E. C. Y. Chung, S.- L. L. Lu, and S. F. Quigley, "Plan of a low idleness asynchronousviper utilizing early consummation recognition," J. Eng. Sci. Technol., vol. 9, no. 6, pp. 755-772,2014.

- 5. J.Sparsø, Prologueto Offbeat Circuit Plan. Lyngby, Denmark: DTUFigure, 2020.

- 6. T.-T.LiuandJ.M.Rabaey,"Factualexaminationandstreamliningofasynchronouscomputer-ized circuits,"inProc.IEEEeighteenth Int.Symp. Offbeat CircuitsSyst.,2012,pp.1-8.

- 7. S.F.Oberman, "Planissuesinsuperiorexecutiondriftingpointarithmaticunits," Ph.D.paper, Dept. Electr. Eng., Stanford Univ., Stanford, CA, USA. 1996.

- 8. J.F.Palmer, B.W.Ravenel, and R.Nave, "Numericinformation processor," Google Licenses USRE 33 629 E, 1982.

- 9. M. R. Pillmeier, M. J. Schulte, and E. G. Walters, III, "Plan alterna#tives for barrel shifters," inProc. Adv. Signal Interaction. Calculations Archit. Execute. Int. Soc. Pick. Photon. XII, vol. 4791,2002, pp. 436-447.

- 10. Plan and Execution of Novel Multiplier utilizing Barrel Shifters Neeta Pandey Delhi Innova-tive College, Saurabh Gupta Delhi Mechanical College, July 2015

- 11. B.K.MohantyandS.K.Patel, "Regiondelay-powerproficientconveyselectviper"

- 12. P.Merollaetal.,"1,000,000Spiking-NeuronCoordinatedCircuitwithaVersatileCorrespon-dence Organization andPointofinteraction," Science, vol.345,no.6197,2014,pp. 668673.

- 13. Stephen H. Unger, Offbeat Consecutive Exchanging Circuits, J. Wiley and Children, Inc., NewYork, NY, 1969.

- 14. D.EMullerandW.C.Bartky,"AHypothesisofasynchronousCircuits,"inRecordsofRegis-tering Research center of Harvard College, 1959, pp. 204-243.

- 15. H. van Gageldonk et al., "An Offbeat Low-Power 80C51 Microcontroller," Proc. Int'l Symp.HighlevelExplorationinOffbeatCircuitsandFrameworks(ASYNC98),IEEECSPress,1998,pp.96-107.

- 16. M. Davies et al., "A 72-Port 10G Ethernet Switch/Switch Utilizing Quasi-Delay-InsensitiveOffbeat Plan," Proc.Intl. Symp. on Offbeat Circuits and Frameworks (ASYNC 14), 2014, pp.103-104.

- 17. J. Teifel and R. Manohar, "Exceptionally Pipelined Offbeat FPGAs," Proc. ACM/SIGDA Int.Symp.on FieldProgrammableDoorExhibits (FPGA04), 2004,pp. 133-142.